Back to Top

ET1816 EtherCAT IP core for Xilinx® FPGAs

One-time kick-off charge for the node-locked quantity-based license for using the freely configurable EtherCAT IP cores on one workstation (no workplace extension possible). Target hardware: selected Xilinx® FPGAs.

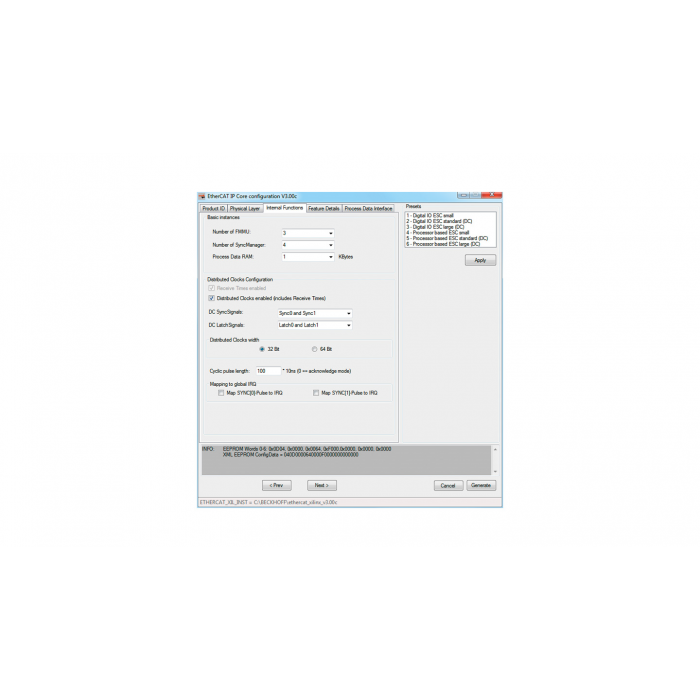

PHY interface: 1…3 ports MII, 1…3 ports RGMII or 1…2 ports RMII

FMMUs : 0…8

SYNC manager: 0…8

DPRAM: 0…60 KB

Distributed clocks: 0…2 SYNC outputs, 0…2 latch inputs (32/64 bit)

Process data interfaces: 32 bit digital I/O, SPI, 8/16 bit asynchronous µC interface, AMBA AXI4/AXI4 LITE interface, 64 bit general purpose I/O

Write Your Own Review

Write your content here...